散熱的惡夢,是半導體的下一個戰場?

- 2025年8月4日

- 讀畢需時 45 分鐘

先進3D封裝技術的演進格局

先進3D封裝的定義:關鍵技術與當前趨勢

傳統的二維 (2D) 晶片佈局已逐漸無法滿足現代電子系統對更高性能、更小尺寸和更多功能的需求,於是,先進封裝技術應運而生,其核心概念是超越平面限制,透過垂直堆疊 (3D) 或高密度水平排列 (2.5D) 多個裸晶和組件於單一封裝體內,以期達到更高的整合度與效能,相較於依賴引線鍵合 (wire bonding) 進行互連的傳統封裝方式,先進封裝採用了更精密的互連技術,目的在縮短訊號傳輸路徑、降低功耗並提升整體系統性能。

關鍵賦能技術:

先進3D封裝的實現依賴於一系列關鍵技術的突破:

矽穿孔 (Through-Silicon Vias, TSVs): TSV是在矽晶圓或裸晶上製作垂直的導電通道,通常填充銅等導電材料,以實現晶片堆疊中不同層級間的電氣連接和熱量傳導,TSV技術顯著縮短了互連距離,提高了整合度和性能,是2.5D和3D架構的基石,它們不僅用於晶片間的直接堆疊,也廣泛應用於中介層 (interposer),作為連接上層晶片和下層基板的橋樑。

微凸塊 (Micro-bumps): 這是指用於裸晶對裸晶 (die-to-die) 或裸晶對中介層 (die-to-interposer) 鍵合的微小焊錫連接點,微凸塊技術是實現先進封裝中高密度互連的關鍵,其尺寸遠小於傳統的C4凸塊,從而允許更多的I/O數量和更短的連接路徑。

重佈線層 (Redistribution Layers, RDLs): RDL是在裸晶或中介層表面製作的精細金屬佈線層,用於將晶片焊墊 (pad) 的I/O連接重新佈局到封裝體上更易於連接的位置,例如微凸塊或焊球陣列,RDL技術使得扇出型封裝成為可能,並為高密度互連提供了靈活性。

主要的先進封裝架構:

基於上述關鍵技術,業界發展出多種先進封裝架構:

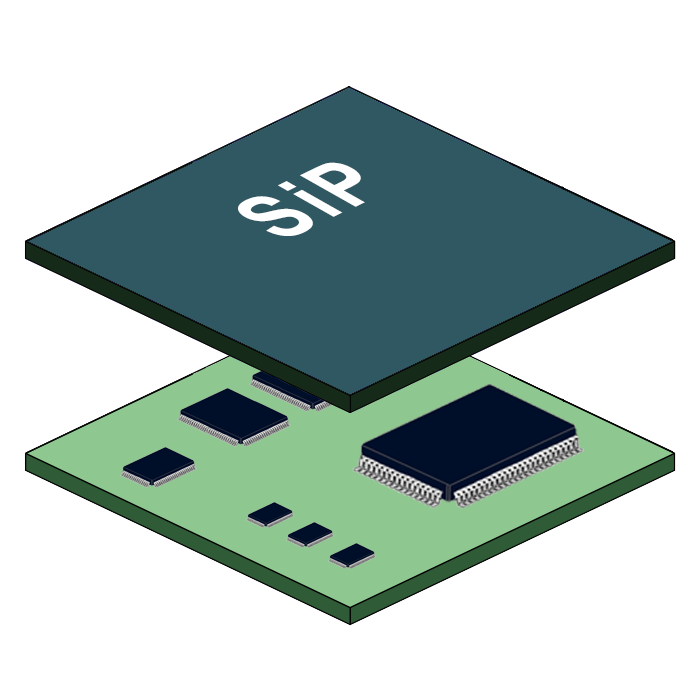

系統級封裝 (System-in-Package, SiP): SiP將多個主動元件 (如處理器、記憶體晶片)、被動元件以及各種功能性器件 (如MEMS、生物晶片、感測器等) 整合在單一封裝體內,3D堆疊技術的進步,進一步推動了SiP向更高整合度和更複雜功能發展。

含處理器、記憶體與儲存元件之單一基板多晶片系統封裝(SiP)的 CAD 圖面。(圖片來源: By Verdel - Own work, CC BY-SA 4.0) 扇出型晶圓級封裝 (Fan-Out Wafer-Level Packaging, FoWLP): FoWLP將單個裸晶嵌入到環氧樹脂模塑料 (Epoxy Mold Compound, EMC) 中,並在裸晶及其周邊區域製作RDL,從而將I/O引腳扇出到裸晶面積之外,這種技術提供了更高的I/O密度、更小的封裝尺寸以及改進的散熱和電氣性能,被視為矽中介層2.5D/3D封裝的一種低成本替代方案。

在扇出型晶圓級封裝(FOWLP)的製程中,依晶片安置的時機與方向不同,常見有三種製程方法。第一種為「晶片朝下、晶片先置」(face down, die first),即晶片在初期即被放入模具中,且其活性面朝下;第二種為「晶片朝上、晶片先置」(face up, die first),此流程同樣於初期放入晶片,但活性面朝上;第三種則是「晶片朝下、晶片後置」(face down, die last),晶片於重布線(RDL)與模塑(molding)等製程後才放入,並以朝下方式定位。這三種策略各有其適用場景與成本效益考量。(圖片來源:By 思考的苇丛 ) CoWoS (Chip-on-Wafer-on-Substrate - 台積電): CoWoS是台積電開發的一種2.5D中介層技術,它將多個裸晶 (如邏輯晶片和高頻寬記憶體 HBM) 並排置於帶有TSV的矽中介層上,然後再將該中介層封裝到基板上,CoWoS技術能夠實現極高的頻寬和優異的整合度,廣泛應用於高性能計算和AI晶片。

SoIC (System-on-Integrated-Chips - 台積電): SoIC是台積電推出的一種前端3D堆疊技術,採用直接銅對銅 (Cu-to-Cu) 混合鍵合 (hybrid bonding) 技術,實現超高密度的垂直互連,SoIC能夠異質整合不同尺寸、功能和製程節點的晶片,其鍵合間距可達次10微米等級,帶來更優異的性能、更低的功耗和更小的尺寸。NVIDIA、AMD和Apple等公司已宣布採用SoIC技術。

英特爾的Foveros和EMIB: Foveros是英特爾的3D裸晶堆疊技術,通常採用主動式中介層和微凸塊進行連接。其衍生技術Foveros Direct則採用銅對銅直接鍵合,EMIB (Embedded Multi-die Interconnect Bridge) 是一種2.5D解決方案,使用小型、局部化的橋接裸晶 (bridge die) 實現高密度裸晶間互連,避免了大型矽中介層的成本和散熱限制。

三星的X-Cube和I-Cube: X-Cube是三星的3D IC封裝技術,包括微凸塊和混合銅鍵合兩種方案。I-Cube則是其2.5D中介層解決方案。

當前發展趨勢:

先進封裝技術正朝著以下幾個主要方向發展:

持續提升整合密度與功能性: 在單一封裝內整合更多、更複雜的功能是主要目標。

小型化與薄型化: 尤其在移動設備和穿戴裝置領域,對更薄、更小封裝的需求持續存在。

異質整合 (Heterogeneous Integration): 將不同製程節點、不同功能甚至來自不同供應商的晶片 (chiplets) 整合在同一封裝內,已成為主流趨勢。這使得系統設計更具靈活性,能夠針對不同功能區塊選擇最優化的製程技術。

追求更高頻寬、更低延遲與更佳功耗效率: 這是滿足AI、HPC等高性能應用需求的關鍵。

關注高密度互連的可靠性: 隨著微凸塊、TSV和混合鍵合的間距不斷縮小,確保這些精細互連結構在複雜應力環境下的長期可靠性,成為研究的重點。

晶片 (Chiplet) 架構的普及: Chiplet已成為先進封裝的基礎構建模組,推動著封裝技術的創新。

值得注意的趨勢是Chiplet的興起所帶來的封裝技術的「普及化」;過去,設計一顆複雜的SoC需要巨大的投入和整合能力,如今,Chiplet的模組化設計,使得不同廠商可以專注於開發特定功能的Chiplet,再透過先進的2.5D/3D封裝平台將它們整合起來;這種模式降低了進入高性能晶片設計的門檻,使得更多小型企業或專注於特定IP的供應商也能參與到複雜系統的構建中,從而激發更廣泛的創新,例如,英特爾的EMIB技術就允許客戶將來自不同晶圓廠的裸晶整合在同一封裝內。

另一個重要的發展是前端製程與後端封裝技術的融合,以台積電的SoIC為例,它被定義為一種「前端」3D堆疊技術,利用晶圓廠等級的製程進行直接銅對銅鍵合,實現了遠小於傳統封裝凸塊間距的超高密度互連;傳統後端封裝的凸塊間距通常在數十微米等級,而SoIC的鍵合間距已進入次10微米範疇,並有望進一步縮小;這種直接鍵合技術,如銅對銅混合鍵合,通常在晶圓級或裸晶對晶圓級進行,需要運用到通常與前端製造相關的先進微影、蝕刻和鍵合能力;這表示要實現下一代3D封裝的互連密度和性能,必須借助前端製造的精度和技術,其深遠影響在於,晶片設計師、晶圓代工廠和封裝廠之間需要更緊密的協同設計和共同開發,或者晶圓代工廠將其服務範圍擴展到傳統上屬於封裝的領域。

下表總結了主要的先進3D/2.5D封裝技術:

表1:先進3D/2.5D封裝技術比較概覽

技術類型 | 關鍵結構特徵 | 主要應用領域 | 主要優勢 | 主要散熱/可靠性考量 |

基於TSV的3D IC | 垂直堆疊裸晶,TSV互連,微凸塊鍵合 | HBM、感測器、部分邏輯-記憶體堆疊 | 極高密度、最短互連、低功耗 | 層間散熱困難、TSV應力、TSV電遷移、堆疊應力 |

CoWoS (台積電) | 2.5D,矽中介層 (含TSV),微凸塊連接邏輯與HBM,再封裝於基板上 | HPC、AI加速器、高階FPGA、網路處理器 | 極高頻寬、異質整合能力、成熟生態系 | 中介層散熱、TIM挑戰、基板翹曲、大型封裝應力 |

SoIC (台積電) | 3D,直接銅對銅混合鍵合,超細間距 (次10µm),無凸塊,晶圓對晶圓 (WoW) 或晶片對晶圓 (CoW) | 高性能邏輯、記憶體堆疊、Chiplet整合 | 極高互連密度、低電氣損耗、小尺寸、異質整合靈活性 | 層間散熱、混合鍵合的對準與應力、薄化晶圓的散熱特性 |

Foveros/EMIB (英特爾) | Foveros: 3D裸晶堆疊 (主動中介層/微凸塊/直接鍵合);EMIB: 2.5D局部橋接裸晶互連 | CPU、GPU、AI晶片、異質整合系統 | Foveros: 高密度堆疊;EMIB: 模組化、成本效益 | Foveros: 堆疊散熱、功耗密度;EMIB: 橋接裸晶與主晶片的熱交互、應力 |

FoWLP | 將裸晶嵌入模塑料,RDL扇出至裸晶外圍,無中介層 | 移動通訊、消費性電子、IoT、電源管理 | 低成本、薄型化、良好的電氣/散熱性能 (相對於傳統WLP) | 模塑料的熱傳導性、RDL應力、翹曲控制 |

X-Cube/I-Cube (三星) | X-Cube: 3D裸晶堆疊 (微凸塊/混合銅鍵合);I-Cube: 2.5D矽中介層 | HBM、行動AP、伺服器CPU | X-Cube: 高頻寬、低功耗;I-Cube: 成熟技術 | X-Cube: 堆疊散熱、混合鍵合可靠性;I-Cube: 中介層散熱 |

驅動力:「超越摩爾定律」時代下AI、HPC與5G的迫切需求

先進3D封裝技術的快速發展,並非偶然,而是多重因素共同作用的結果;其中,最根本的驅動力來自於傳統摩爾定律的趨緩。數十年來,半導體產業遵循著摩爾定律的指引,即積體電路上的電晶體數量約每18至24個月翻倍,從而帶來持續的性能提升和成本下降;然而,隨著電晶體尺寸逼近原子級別,進一步微縮面臨著巨大的物理挑戰和經濟成本壓力;在這樣的背景下,「超越摩爾定律」(More than Moore) 的概念應運而生,先進封裝技術,特別是3D整合,成為延續性能增長曲線、實現更高系統整合度的關鍵途徑。

與此同時,一系列新興應用對晶片性能、功耗和尺寸提出了前所未有的嚴苛要求,進一步加速了先進封裝技術的導入:

人工智慧 (AI) 與機器學習 (ML): AI和ML應用,尤其是深度學習模型,需要進行大規模的q平行計算,並對記憶體頻寬和延遲有著極高的要求,3D整合技術,特別是將高頻寬記憶體 (HBM) 與邏輯晶片進行堆疊,能夠顯著提升數據傳輸速率、降低延遲,從而滿足AI運算對海量數據吞吐的需求。

高性能計算 (HPC): HPC領域的需求與AI相似,同樣追求極致的運算能力和高速的數據交換。先進封裝透過高密度整合和優化的互連方案,為HPC系統提供了強大的支援。

5G/6G 通訊: 新一代通訊技術要求更小的設備尺寸、更高的工作頻率以及整合更多樣化的組件 (如射頻、模擬、數位電路)。先進封裝技術,如SiP和FoWLP,能夠在緊湊的空間內實現這些複雜功能的高度整合。

汽車電子、物聯網 (IoT)、邊緣計算、穿戴裝置: 這些應用場景對晶片的微型化、功耗效率以及整合感測器等其他功能有著強烈需求。先進封裝技術能夠滿足這些多樣化的需求,推動著相關產業的發展。

3D/2.5D 整合的核心優勢:

相較於傳統的2D平面封裝,3D/2.5D整合技術帶來了多方面的顯著優勢:

縮短互連長度: 透過垂直堆疊或緊密並排,晶片間的訊號傳輸路徑大幅縮短,從而降低了訊號延遲和功耗,同時提升了數據傳輸頻寬。

更小的佔板面積/封裝尺寸: 垂直堆疊顯著減少了晶片在印刷電路板 (PCB) 上的佔用面積,使得終端產品更加輕薄短小。

實現異質整合: 這是3D/2.5D封裝最具吸引力的優勢之一。它允許將不同製程節點、不同功能 (如邏輯、記憶體、感測器、射頻)、甚至來自不同製造商的晶片整合在同一封裝內,實現了系統級的最佳化設計。

垂直整合架構下日益嚴峻的散熱困境

隨著先進3D封裝技術將越來越多的電晶體和功能單元整合到日益縮小的空間內,熱管理問題已成為阻礙其性能進一步提升和可靠性保障的關鍵瓶頸。這種「散熱夢魘」源於多方面物理因素的疊加效應。

熱量產生的物理學:功率密度攀升與熱點叢生

3D整合架構的本質是透過垂直堆疊多個主動裸晶或在2.5D配置中高密度封裝它們,這不可避免地導致單位體積內的功耗急劇上升,即功率密度顯著增加;例如,在一些2.5D封裝平台中,熱通量已超過 100W/cm2,而微處理器的功率密度也從約 40W/cm2 攀升至 100W/cm2 左右;更有甚者,一些先進冷卻技術的演示目標已指向 350W/cm2 的平均功率密度和超過 2kW/cm2 的局部熱點功率密度;未來,功率密度預計將持續上升,部分應用甚至可能達到 500W/cm2 的水平。

與此同時,異質整合的特性使得封裝體內不同晶片或同一晶片內不同功能區塊的功耗可能存在巨大差異,這導致在局部區域產生溫度遠高於平均晶片溫度的「熱點」(hot spots),這些熱點如同潛伏的火山,對晶片的性能和可靠性構成嚴重威脅,例如,在記憶體與邏輯晶片堆疊的結構中,熱點的位置會根據是記憶體在邏輯之上 (MoL) 還是邏輯在記憶體之上 (LoM) 而發生轉移。

雪上加霜的是,為了實現3D堆疊和TSV的形成,矽晶圓通常需要進行薄化處理,然而,薄化後的矽晶圓其熱導率會隨厚度減小而降低,這表示著晶片本身的橫向導熱能力減弱,使得熱量更難從熱點區域擴散出去,進一步加劇了晶片內部的熱阻,阻礙了有效的散熱。

這種功率密度攀升、矽晶圓薄化導致導熱能力下降以及熱傳導路徑複雜化(詳見後述)的組合,形成了一個極具挑戰性的散熱局面,高功率密度產生的大量熱量,被困在導熱性能變差的薄化晶片內,並且難以透過日益複雜的垂直路徑有效傳導至外部冷卻系統,這種協同的負面效應使得熱點問題更加突出,溫度更高,也更難以降溫。

複雜散熱路徑的導航與熱串擾管理

在3D封裝結構中,熱量從產生源頭到最終散逸至外部環境,需要穿越一條漫長而曲折的路徑,這條路徑包含了多層矽晶片、熱介面材料 (Thermal Interface Materials, TIMs)、中介層、基板等,每種材料都具有不同的熱導率,且各材料間的介面也存在熱阻,這種複雜的熱傳導路徑往往效率低下,容易形成散熱瓶頸,例如,在2.5D封裝中,熱量可能需要先經過TIM1、中介層、TIM2,然後才能到達散熱器,在3D堆疊中,所有層級晶片產生的熱量共享一條共同的、更長的散熱路徑,使得熱梯度更加陡峭。

每個材料介面,如裸晶與TIM之間、TIM與散熱片之間、裸晶與中介層之間,都會引入介面熱阻 (Thermal Interface Resistance, TIR),TIR的存在會阻礙熱量的順暢流動。在包含眾多介面的3D堆疊結構中,累積的TIR效應可能非常顯著,成為整體散熱性能的主要限制因素之一。

更為棘手的是熱串擾 (thermal crosstalk) 問題,在高度整合的異質系統中,一個晶片或裸晶產生的熱量會顯著影響相鄰或垂直堆疊的其他組件的溫度和性能,例如,在2.5D封裝中,為了確保訊號完整性和電源完整性,邏輯晶片和HBM通常被放置在彼此非常近的距離 (如500微米以內),這使得邏輯晶片產生的熱量很容易傳導到對溫度更為敏感的HBM上,導致HBM漏電流增加、性能下降甚至壽命縮短;這種熱串擾效應,如果管理不當,可能會抵消異質整合所帶來的性能或可靠性優勢,這表示在進行Chiplet佈局時,不僅要考慮電氣連接,更需要將熱隔離策略納入考量,例如策略性地增加Chiplet間距,或採用低熱導率的模塑料作為熱屏障。

互連、TSV與功率傳輸網路 (PDN) 中的焦耳熱貢獻

除了晶片本身的有功功率消耗外,電流流過導體時產生的焦耳熱 (Joule heating, I2R 損耗) 也是3D封裝中一個不可忽視的熱源,尤其是在互連結構、TSV以及功率傳輸網路 (PDN) 中。

隨著互連線寬的縮小和電流密度的增加,RDL、微凸塊以及晶片內部佈線中的焦耳熱效應日益顯著。高電流密度流經TSV時,同樣會產生可觀的焦耳熱,這不僅增加了整體熱負載,還可能在TSV內部或周邊區域形成局部熱點。

PDN的效率也直接影響熱量的產生。PDN中的電阻,包括用於功率傳輸的TSV,都會因電流流過而產生焦耳熱。更重要的是,焦耳熱是一個與溫度耦合的問題。導體的電阻率會隨溫度升高而增加,這表示焦耳熱的產生會導致局部溫度上升,進而使導體電阻進一步增加,在相同電流下產生更多的焦耳熱。這種正反饋效應如果控制不當,甚至可能引發熱失控 (thermal runaway)。因此,準確的電熱協同模擬 (electro-thermal co-simulation) 對於預測和管理先進封裝中的溫度至關重要,單純的熱模擬可能會低估焦耳熱的影響。

下表總結了先進3D封裝中的主要散熱挑戰:

表2:先進3D封裝中的主要散熱挑戰

散熱挑戰 | 現象描述 | 3D架構中的主要促成因素 | 典型報告量級/影響 |

高功率密度 (High Power Density) | 單位體積內功耗顯著增加,導致整體發熱量巨大。 | 多個主動裸晶的垂直堆疊或高密度2.5D排列。 | >100W/cm2, 熱點可達 >2kW/cm2, 未來或達 500W/cm2。 |

局部熱點 (Localized Hot Spots) | 由於異質整合和功能區塊功耗差異,在封裝體內形成溫度遠高於平均值的局部高溫區域。 | 不同晶片/功能區塊的功耗不均勻,薄化矽晶圓降低橫向導熱能力。 | 熱點溫度可能比平均晶片溫度高出數十度,熱點功率密度可達 1000W/cm2。 |

複雜/高阻抗散熱路徑 | 熱量需穿過多層不同熱導率的材料和介面,形成曲折且熱阻較高的散熱通道。 | 多層堆疊結構 (矽、TIM、中介層、基板),每個介面都存在介面熱阻 (TIR)。 | 總熱阻顯著增加,限制散熱效率。 |

熱串擾 (Thermal Crosstalk) | 一個晶片或裸晶產生的熱量影響相鄰或堆疊的其他組件的溫度和性能。 | 高密度封裝,異質組件間的近距離佈置 (如邏輯晶片與HBM間距 <500μm)。 | 可能導致敏感組件 (如記憶體) 漏電流增加、性能下降。 |

互連/TSV中的焦耳熱 | 電流流過RDL、微凸塊、TSV等互連結構時產生的 I2R 熱量,成為額外的熱源。 | 互連尺寸縮小、電流密度增加、材料電阻率的溫度依賴性。 | 焦耳熱貢獻日益顯著,可能導致局部過熱甚至熱失控。 |

熱應力下的可靠性:熱機械與電氣退化

先進3D封裝在追求極致性能的同時,其複雜的結構和嚴峻的熱環境也對封裝的長期可靠性構成了前所未有的挑戰。高溫和溫度循環不僅會加速材料老化,還會引發顯著的熱機械應力,導致各種結構性失效。此外,電遷移等電氣退化機制在高溫和高電流密度下也更為活躍。這些因素共同作用,可能導致封裝性能不穩定、壽命縮短,甚至災難性失效。

材料退化機制:介電質、熱介面材料與焊錫互連的老化

在持續的高溫或反覆的溫度波動下,構成3D封裝的各種材料會逐漸發生物理和化學性質的改變,即材料老化,從而影響其功能和封裝的整體可靠性。

介電材料老化: 在後段製程 (BEOL) 和中介層中廣泛使用的低介電常數 (low-k) 和超低介電常數 (ultra-low-k) 材料,如SiOCH和SiOx,在熱應力和溫度循環作用下容易發生退化。其退化機制包括:化學鍵斷裂與重組 (例如SiOx中矽醇基的縮合反應)、懸垂基團 (pendant groups) 的降解 (例如SiOCH中的烷基鏈斷裂)、材料孔隙率的改變以及內部缺陷的演化。這些微觀結構的變化會直接影響介電材料的宏觀電氣特性,如介電常數的漂移和插入損耗的增加,進而影響訊號完整性和高速性能。

熱介面材料 (TIM) 退化: TIM作為填充晶片與散熱器之間微小氣隙、降低接觸熱阻的關鍵材料,其長期穩定性至關重要。然而,常見的TIM材料,如導熱膏、導熱凝膠、導熱墊片和相變化材料,在長期高溫工作或溫度循環下,可能會出現「泵出」(pump-out,材料從介面被擠出)、「乾涸」(dry-out,液態組分揮發或分離)、「空洞形成」(voiding)、「開裂」(cracking) 以及與接觸表面「附著力喪失」(loss of adhesion) 等現象。這些退化會導致TIM的有效熱導率下降,介面熱阻增加,從而削弱散熱效果,使晶片溫度升高。即使是性能較好的凝膠型TIM,也可能在BGA回焊或表面貼裝技術 (SMT) 組裝過程中因膨脹而產生問題。

焊錫凸塊/互連退化: 微凸塊和BGA焊球等焊錫接點是3D封裝中主要的電氣和機械連接結構。在溫度循環和高電流密度的雙重作用下,這些焊點容易發生疲勞、蠕變、介金屬化合物 (Intermetallic Compound, IMC) 過度生長以及空洞形成等退化現象。高溫會加速IMC的生長速率,過厚的IMC層通常較脆,容易開裂。同時,高溫和高電流密度也會促進焊點內部空洞的形核與長大,最終可能導致電阻增加甚至開路。

機械應力與失效:翹曲、開裂、分層與凸塊疲勞

不同材料之間熱膨脹係數 (Coefficient of Thermal Expansion, CTE) 的失配是3D封裝中熱機械應力的主要來源。當封裝體經歷溫度變化時 (如製造過程中的降溫冷卻、或實際工作中的功率循環),CTE失配會導致內部各組件產生不同程度的膨脹或收縮,從而引發應力集中,並可能導致一系列機械失效模式。

封裝/裸晶翹曲 (Warpage): CTE失配會導致整個封裝體或個別裸晶發生彎曲變形,即翹曲。嚴重的翹曲不僅會影響後續的組裝工藝 (如散熱器安裝),還可能導致焊點連接失效 (例如BGA球開路)、TIM接觸不良等問題。研究表明,基板厚度、材料選擇 (如低CTE的基板和底部填充劑 Underfill) 以及晶片與封裝的尺寸比例都會影響翹曲程度。

開裂 (Cracking) 與分層 (Delamination): 長期累積的熱機械應力一旦超過材料的斷裂強度或介面結合強度,就會導致開裂或分層。開裂可能發生在裸晶本身、中介層、介電層、底部填充劑等部位。分層則常發生在不同材料的介面處,例如TSV與周圍介電層的介面、裸晶與底部填充劑的介面等。

焊點疲勞 (Solder Joint Fatigue / Bump Fatigue): 在反覆的溫度循環作用下,焊錫凸塊會經歷應力應變的循環加載,從而引發疲勞損傷。這通常表現為疲勞裂紋的萌生和擴展,最終導致焊點的電氣連接斷開。這是一種典型的蠕變-疲勞交互作用機制。底部填充劑的使用可以有效地分散應力,提高焊點的抗疲勞壽命。

電遷移:對互連完整性的持續威脅,尤其在TSV中

電遷移 (Electromigration, EM) 是指導體材料中的金屬原子在強電場和電子流動的衝擊下發生質量遷移的現象。在高電流密度、高溫梯度和機械應力的共同作用下,電遷移問題尤為突出。電遷移會導致金屬導體中某些區域原子虧空形成空洞 (voids),造成開路;而在另一些區域原子堆積形成小丘 (hillocks),可能導致短路。

TSV中的電遷移: TSV由於其特殊的幾何結構和工作環境,成為電遷移的高發區域。首先,TSV可能承載較高的電流密度。其次,TSV與其頂部和底部的連接焊盤 (landing pads) 或佈線之間往往存在顯著的尺寸不匹配,容易造成電流擁擠和應力集中。更重要的是,TSV自身因CTE失配引起的熱機械應力會與電遷移產生交互作用,進一步加速失效進程。研究表明,TSV周圍的應力梯度對其電遷移壽命有顯著影響。

其他互連結構中的電遷移: 微凸塊和RDL等互連結構在高電流密度和高工作溫度下同樣面臨電遷移的挑戰。在焊錫凸塊中,電流擁擠現象會加速IMC反應,並導致陽極端IMC增厚、陰極端形成空洞和裂紋,同時產生溫度梯度引發熱遷移 (thermal migration),電遷移與熱遷移的共同作用會加速焊點失效。

TSV作為3D整合的核心組件,其可靠性對整個封裝至關重要。它們不僅承受著由於矽與填充金屬 (通常是銅) 之間CTE失配引起的巨大熱機械應力,同時也是電遷移的高風險點。這種雙重壓力使得TSV成為3D封裝可靠性鏈條中的薄弱環節。因此,TSV的設計 (如幾何形狀、材料選擇) 和製造工藝 (如介面質量控制) 對於確保3D封裝的長期穩定運行具有決定性意義。

對性能穩定性的影響:時序餘裕縮減與漏電流增加

高溫和熱點不僅直接威脅封裝的物理完整性,還會對晶片的電氣性能和穩定性產生顯著的負面影響。

溫度對元件/互連延遲的影響: 半導體元件的載流子遷移率和互連導線的電阻率都對溫度敏感。溫度升高會導致載流子遷移率下降、電阻率增加,從而使得邏輯閘延遲和互連線RC延遲增大。這種延遲的增加會壓縮電路的時序餘裕 (timing margin),嚴重時可能導致時序違規 (timing failure),迫使設計者採用更保守的時序設計,從而犧牲了部分性能。

漏電流增加: 晶片的漏電流 (包括次閾值漏電流和柵極漏電流) 對溫度呈指數級敏感關係。工作溫度的升高,特別是局部熱點的存在,會導致漏電流急劇增加。漏電流的增加不僅增大了晶片的靜態功耗,更重要的是,它本身也會產生熱量,進一步推高晶片溫度。這種「溫度-漏電流」的正反饋循環,如果不能得到有效控制,輕則導致功耗超標、性能下降,重則可能引發熱失控,造成永久性損壞。這種熱反饋迴路不僅有熱失控的風險,還會持續惡化性能,因為它會增加延遲並縮小時序裕度,使得穩定操作成為一個動態變化的目標。

熱點對性能和穩定性的影響: 局部熱點會導致受影響區域的性能嚴重下降,局部時序餘裕縮小,並對整體漏電流產生不成比例的貢獻。由於傳統的表面冷卻方式可能無法有效冷卻深埋在3D結構內部的熱點,因此需要更具針對性的熱管理策略。

這些熱引發的退化機制往往不是孤立發生的,而是相互交織、相互促進的。例如,高溫加速了TIM的老化,劣化的TIM導致更高的晶片溫度,這又加劇了CTE失配應力,可能引發翹曲或開裂,同時也促進了互連結構中的電遷移。這種複雜的耦合效應使得3D封裝的可靠性預測和緩解措施變得極具挑戰性,需要綜合考慮多種物理場的交互作用。

下表系統地記錄了熱應力下3D封裝的主要可靠性失效機制:

表3:熱應力下3D封裝的主要可靠性失效機制

失效機制 | 物理過程描述 | 3D堆疊中受影響的組件/材料 | 主要應力源 | 典型表現/後果 |

介電材料老化 (SiOCH/SiOx) | 熱應力下化學鍵變化、懸垂基團降解、孔隙率改變、缺陷演化。 | BEOL介電層、中介層介電質 | 高溫浸泡、溫度循環 | 介電常數漂移、插入損耗增加、訊號完整性下降。 |

TIM退化 (泵出/乾涸) | 材料從介面擠出、液態組分揮發/分離、空洞形成、開裂、附著力喪失。 | TIM1 (裸晶-散熱蓋/片), TIM2 (散熱蓋/片-散熱器) | 高溫浸泡、溫度循環、機械應力 | 介面熱阻增加、散熱效率下降、晶片溫度升高。 |

焊點疲勞/蠕變 (BGA球/微凸塊) | 溫度循環下應力應變循環加載導致裂紋萌生與擴展;高溫下持續應力導致永久變形。 | BGA焊球、微凸塊、C4凸塊 | 溫度循環、CTE失配、高電流密度 (加速蠕變) | 電阻增加、電氣開路、機械連接失效。 |

封裝/裸晶翹曲 | 不同材料CTE失配導致封裝體或裸晶在溫度變化時發生彎曲變形。 | 整個封裝體、裸晶、基板、中介層 | 製造過程中的溫度變化、工作中的溫度循環、CTE失配 | 組裝困難、焊點開路、TIM接觸不良、可靠性下降。 |

介面分層 (TSV/底部填充劑) | 應力超過介面結合強度導致不同材料層分離。 | TSV-介電層介面、裸晶-底部填充劑介面、層間介電質介面 | 溫度循環、CTE失配、製造缺陷 | 電氣連接失效、散熱路徑中斷、結構完整性破壞。 |

裸晶/中介層開裂 | 應力超過材料斷裂強度導致裂紋產生。 | 矽裸晶、矽/玻璃中介層、介電層 | 熱機械應力、CTE失配、製造缺陷 | 晶片功能失效、電氣開路。 |

TSV中的電遷移 | 高電流密度和溫度下,TSV填充金屬 (如銅) 原子沿電子流方向遷移,形成空洞或小丘。 | TSV填充金屬、TSV與焊盤/佈線的介面 | 高電流密度、高溫、熱機械應力、幾何尺寸不匹配 | TSV電阻增加、開路或短路,影響3D堆疊的垂直互連。 |

凸塊/RDL中的電遷移 | 微凸塊和RDL在高電流密度和溫度下發生類似的原子遷移現象。 | 微凸塊、RDL導線 | 高電流密度、高溫、電流擁擠 | 互連電阻增加、開路或短路。 |

熱管理創新:當前策略與新興解決方案

面對3D封裝日益嚴峻的散熱挑戰,學術界和工業界正積極探索和開發各種創新的熱管理策略。這些策略涵蓋了從材料科學的突破到先進冷卻系統的整合,重點在有效地將熱量從高功率密度的封裝中移除,保障其性能和可靠性。

熱介面材料 (TIMs):進展、性能局限與退化挑戰

熱介面材料 (TIMs) 在電子封裝散熱中扮演著至關重要的角色。它們被用於填充晶片、散熱片 (heat spreader) 和散熱器 (heat sink) 之間存在的微觀氣隙,從而降低接觸熱阻,為熱量提供一個低阻抗的傳導路徑。在典型的封裝結構中,存在TIM1 (位於裸晶與散熱蓋/散熱片之間) 和TIM2 (位於散熱蓋/散熱片與外部散熱器之間)。

目前市場上存在多種類型的TIM,包括導熱膏、導熱凝膠、導熱墊片、相變化材料 (PCMs)、焊錫基TIM、液態金屬以及新興的奈米複合材料。選擇TIM時,需要綜合考量其整體熱導率 (bulk thermal conductivity)、施加後的鍵合層厚度 (Bond Line Thickness, BLT)、接觸熱阻、以及在溫度循環和高溫環境下的長期可靠性。

儘管TIM技術不斷進步,但其性能和可靠性仍面臨挑戰。如前所述,TIM材料在高溫和溫度循環下容易發生泵出、乾涸、空洞形成、開裂等退化現象,導致介面熱阻隨時間增加。特別是對於非鍵合型的TIM (如導熱膏),這些問題更為常見。焊錫基TIM雖然初始熱性能優異,但在高溫下容易發生蠕變。確保整合散熱片下TIM的質量通常需要透過掃描聲學斷層掃描 (SAT) 等非破壞性檢測手段進行監控。

為了克服這些限制,研究人員正致力於開發新型TIM。例如,奈米複合TIM,如利用塗覆銀的奈米纖維網絡與銦基體複合而成的Nano-TIM,展現出與純銦相當的低熱阻,同時具有更優的機械性能。此外,自組裝的砷化硼複合材料因其高熱導率和良好的機械柔順性也顯示出應用潛力。碳奈米管 (CNT) 陣列TIM也因其優異的熱和機械性能而被視為未來有前景的材料,但其鍵合技術仍需進一步開發。

散熱片:從傳統材料到先進複合材料 (如鑽石、氮化硼)

散熱片 (heat spreader) 的主要功能是將來自小型裸晶或局部熱點的集中熱量擴散到更大的面積上,從而降低傳遞給TIM2和外部散熱器的熱通量,提高整體散熱效率。

傳統的散熱片材料主要為銅和鋁,因其具有較高的熱導率和良好的加工性。許多封裝件中會整合散熱片 (Integrated Heat Spreader, IHS)。

隨著對散熱性能要求的提高,研究重點轉向具有更高熱導率的先進材料和複合材料:

六方氮化硼 (hBN): hBN具有高熱導率和優良的電絕緣性,非常適合用作散熱片材料,既能有效散熱,又能保持電氣隔離。透過液相剝離等方法可以製備hBN奈米片,並將其製成柔性均勻的hBN薄膜散熱片。

鑽石: 鑽石是目前已知具有最高熱導率的材料。多晶鑽石 (Polycrystalline Diamond, PCD) 散熱片以及整合在後段製程 (BEOL) 中的鑽石矩陣支架,在橫向散熱和降低熱點溫度方面展現出巨大潛力。PCD的熱導率可達到 500−1800W/mK。

石墨烯-碳奈米管 (G-CNT) 混合散熱片/散熱器: 這種複合材料結合了二維石墨烯優異的橫向導熱能力和一維碳奈米管增強的對流/垂直傳熱能力,有望實現高效的多維散熱。

帶有穿透玻璃孔 (TGV) 的玻璃中介層: 玻璃材料具有良好的熱穩定性和與矽相近的低CTE。在中介層中整合TGV可以顯著提高局部熱導率,例如從純玻璃的約 1.2W/mK 提升至約 94W/mK,為管理先進電子封裝中的散熱挑戰提供了新途徑。

散熱片的優化策略涉及材料選擇、幾何形狀設計以及與TIM和冷卻方案的整合。增材製造 (Additive Manufacturing, AM) 技術為製造具有複雜幾何形狀的散熱片開闢了新的可能性。

嵌入式與先進冷卻技術

隨著功率密度的持續攀升,傳統的風冷和間接液冷方案逐漸捉襟見肘。為了應對極端散熱需求,一系列更直接、更高效的嵌入式和先進冷卻技術應運而生。

微流控與晶片上液體冷卻:

概念: 這種技術的核心思想是將液體冷卻劑直接引入到晶片內部或晶片之間,透過在矽裸晶或中介層中蝕刻微通道 (microchannels) 或微間隙 (microgaps),或者利用堆疊裸晶間的空隙,使冷卻劑流過熱點區域,直接帶走熱量。

類型: 包括單相液冷和相變液冷 (利用液體沸騰時吸收大量潛熱,傳熱效率更高)。為了避免電氣問題,通常選用介電性質的冷卻液。

性能: 微流控冷卻能夠應對極高的功率密度,例如已證實可冷卻 350W/cm2 的平均功率密度和超過 2kW/cm2 的熱點,以及高達 2870W/cm3 的體積熱流密度,並能顯著降低晶片溫度。

製造與整合挑戰: 儘管前景廣闊,但微流控冷卻的實現面臨諸多挑戰,包括複雜的製造工藝 (如深反應離子蝕刻 DRIE、晶圓鍵合)、與TSV的整合、流體歧管設計、泵送功率消耗、流體連接的可靠性、成本以及大規模量產的可擴展性等。IMEC等研究機構正在探索使用增材製造陶瓷 (如SiC) 冷卻器來應對這些挑戰。

浸沒式冷卻 (Immersion Cooling):

概念: 將整個電子組件或伺服器完全浸沒在介電液體中,利用液體的對流和/或相變來帶走所有表面的熱量。

可行性與優勢: 對於高密度數據中心等應用,浸沒式冷卻具有高效散熱、降低風扇能耗的潛力,並可能透過減少氧化和灰塵污染來提高系統可靠性。

挑戰: 主要挑戰包括材料兼容性 (介電液體可能影響PCB的楊氏模量、玻璃轉化溫度等物理特性)、液體密封、維護、成本以及缺乏廣泛的長期可靠性數據等。

噴射衝擊冷卻 (Jet Impingement Cooling):

概念: 將高速流體噴射流 (液體或氣體) 直接衝擊到高溫表面,利用極高的局部傳熱係數進行冷卻。

有效性: 能夠實現極高的傳熱係數,非常適合針對性地冷卻強烈的局部熱點。已有研究展示了超過 250kW/m2K 的傳熱係數,可冷卻高達 5500W/cm2 的熱通量。

挑戰: 冷卻均勻性、流體管理、噴嘴堵塞、表面侵蝕、整合複雜性、可擴展性和成本是主要障礙。增材製造技術被用於製造複雜的噴射衝擊冷卻器結構。

微型與扁平熱管 (Miniature and Flat Heat Pipes):

概念: 熱管是一種被動的兩相傳熱器件,利用密封結構內工作流體的蒸發和冷凝來高效傳輸熱量。扁平或微型熱管可以嵌入到PCB或封裝基板內部,實現高效的熱量擴散。

製造與性能: 可以利用PCB製造工藝或3D打印技術來製造。它們能提供遠高於固體導熱材料的等效熱導率,例如有報導稱其等效熱導率可達固體銅的七倍以上。

挑戰: 毛細芯結構設計、工作流體選擇、密封性、在小尺寸內的整合以及嵌入式版本的製造複雜性是主要挑戰。

導熱矽穿孔 (TTSVs) 與熱收集網路 (TCNs) 的關鍵作用

除了上述外部或嵌入式冷卻方案外,在晶片內部優化導熱路徑也是熱管理的重要一環。導熱矽穿孔 (Thermal Through-Silicon Vias, TTSVs) 和熱收集網路 (Thermal Collection Networks, TCNs) 正是為此目的而設計的。

導熱矽穿孔 (TTSVs): TTSV是專門設計用於導熱的TSV,它們為埋在3D堆疊深處的裸晶或局部熱點提供低熱阻的垂直導熱通路,將熱量有效地傳導至上層的散熱片或散熱器。

熱收集網路 (TCNs): TCN是在晶片後段製程 (BEOL) 層中設計的金屬走線網路,用於從分佈式的熱源 (如邏輯電路) 收集熱量,並將其匯集到TTSV,再由TTSV傳導出去。

有效性與對熱預算的影響: 研究表明,TTSV和TCN的結合能夠顯著降低晶片最高溫度,有效移除熱點區域的熱量。例如,在一項研究中,採用TCN和TTSV的3D IC結構,其熱點區域的熱量吸出效率比傳統方案提高了11%至35%。

挑戰: 實施TTSV和TCN也面臨一些挑戰,包括佔用晶片面積 (area overhead)、與周圍矽或介電材料的CTE失配問題、如果設計不當可能導致大面積過熱,以及增加了製造的複雜性。

優化: TTSV的佈局 (位置、密度)、直徑、間距、深寬比以及填充材料 (如銅與碳奈米管的比較) 都是影響其導熱性能的關鍵設計參數,需要仔細優化。

新型熱管理材料:碳基奈米材料與鑽石基板/矩陣支架

材料科學的進步為解決3D封裝的散熱難題提供了新的思路。其中,碳基奈米材料和鑽石材料因其卓越的熱性能而備受關注。

碳基奈米材料 (CNTs, 石墨烯):

特性: 碳奈米管 (CNTs) 和石墨烯都具有極高的本徵熱導率和優良的機械強度。CNTs因其一維結構,非常適合用於垂直方向的熱量傳輸;而二維的石墨烯則擅長於面內的橫向熱量擴散。

應用:

奈米複合TIMs: 將CNTs或石墨烯作為填料加入傳統TIM基體中,可以顯著提高其熱導率。

基於CNT的TSVs: 相較於傳統的銅TSV,CNT填充的TSV具有更低的CTE,能更好地匹配矽的熱膨脹,同時在高電流密度下表現出更優的抗電遷移能力。

石墨烯-CNT混合散熱片/散熱器: 結合兩者的優勢,實現高效的多維散熱。

CNT陣列TIMs: 利用垂直排列的CNT陣列作為TIM,有望實現極低的介面熱阻。

挑戰: 儘管前景廣闊,但碳基奈米材料在實際應用中仍面臨介面熱阻高、大規模可控制備困難、成本較高以及與標準CMOS製程整合相容性等問題。

鑽石基板/矩陣支架:

特性: 鑽石擁有已知材料中最高的室溫熱導率 (多晶鑽石PCD可達 500−1800W/mK),同時具有良好的電絕緣性 (低介電常數) 和與矽之間較低的熱邊界電阻 (Thermal Boundary Resistance, TBR)。

應用: 研究表明,可以在BEOL製程中兼容地生長兩層PCD矩陣支架,作為銅導熱孔的替代品,用於垂直導熱。同時,PCD層也可以作為高效的橫向散熱層,整合在層間介電質 (Interlayer Dielectric, ILD) 中。

性能: 實驗證明,整合鑽石矩陣支架能夠顯著降低3D IC中的熱點溫度,並使溫度分佈更加均勻。

製造與挑戰: 低溫化學氣相沉積 (CVD) 生長高質量PCD、PCD薄膜的拋光平坦化、與現有BEOL製程的整合以及殘餘應力管理是主要的製造挑戰。

從上述多樣化的解決方案可以看出,3D封裝的熱管理並無「萬靈丹」。每種技術都有其特定的適用場景、優勢和局限性。例如,噴射衝擊冷卻可能適用於應對極端的局部熱點,而浸沒式冷卻則更適合大型系統的整體散熱,嵌入式微流控則專注於直接的裸晶冷卻。因此,未來的熱設計很可能需要採取一種「多模式」或「工具箱」的方法,根據具體的應用需求、功率水平、成本限制和外形尺寸等因素,靈活地組合和定製多種熱管理技術。這也表示系統級的協同優化和設計將變得更加重要。

同時,對碳奈米材料和鑽石等新型材料的深入研究,標誌著材料科學的突破在熱管理領域正扮演著與冷卻硬體工程創新同等重要的角色。這些先進材料的合成、加工以及規模化整合能力,將是決定未來熱管理技術上限的關鍵因素之一。然而,儘管微流控和嵌入式熱管等高效冷卻方案在實驗室中取得了令人鼓舞的成果,但它們通往大規模量產 (High-Volume Manufacturing, HVM) 的道路仍然充滿挑戰,涉及成本、複雜性、可靠性以及與現有半導體製造流程的整合等問題。增材製造技術為此提供了一些新的可能性,但其自身在封裝領域的規模化應用和材料限制也尚待克服。如何經濟高效且可靠地大規模生產這些複雜的冷卻方案,是解鎖3D IC全部潛力的核心障礙之一。

下表對先進3D IC的熱管理解決方案進行了比較分析:

表4:先進3D IC熱管理解決方案比較分析

解決方案類別 | 具體實例/材料 | 工作原理 | 報告有效性 (例如:冷卻功率密度,ΔT降低,k_eff) | 主要優勢 | 主要挑戰 (包括整合、成本、HVM、可靠性) |

先進TIMs | 奈米複合TIM (如Ag-奈米纖維/銦), 自組裝砷化硼複合材料, CNT陣列TIM | 填充介面微觀氣隙,降低接觸熱阻,提供高效導熱通路。 | Nano-TIM熱阻 2.1K⋅mm2/W。砷化硼複合材料熱導率 21W/mK。 | 顯著降低介面熱阻,提高導熱效率。 | 材料穩定性、長期可靠性 (泵出、乾涸)、成本、與不同表面的兼容性、可製造性。 |

新型散熱片 | 六方氮化硼 (hBN), 多晶鑽石 (PCD), 石墨烯-CNT混合材料, 帶TGV的玻璃中介層 | 利用高熱導率材料將集中熱量橫向擴散到更大面積。 | hBN有效降低熱點溫度約 20∘C。PCD熱導率 500−1800W/mK。玻璃+TGV局部熱導率可達 94W/mK。 | 優異的熱擴散能力,可降低熱流密度,部分材料兼具電絕緣性。 | 材料成本 (尤其是鑽石)、製造工藝複雜性、與其他封裝材料的CTE匹配、機械強度。 |

微流控/晶片上液冷 | 單相/兩相微通道冷卻, 介電冷卻液 | 使冷卻液直接流過晶片內部或層間的微通道/微間隙,高效移除熱量。 | 可冷卻 >350W/cm2,熱點 >2kW/cm2,體積熱流密度 2870W/cm3。 | 極高的散熱效率,可直接冷卻熱點。 | 製造複雜 (蝕刻、鍵合)、流體歧管設計、泵送功耗、密封與洩漏風險、長期可靠性、成本、HVM可擴展性。 |

浸沒式冷卻 | 單相/兩相介電液體浸沒 | 將整個電子系統浸沒在介電冷卻液中,透過自然/強制對流或相變散熱。 | 適用於高密度數據中心,可顯著降低冷卻能耗。 | 整體散熱效果好,可降低風扇噪音和功耗。 | 材料兼容性 (液體對PCB/組件的影響)、液體洩漏與維護、系統複雜性、成本、缺乏長期可靠性數據。 |

噴射衝擊冷卻 | 高速液體/氣體噴射流 | 將高速流體直接衝擊熱表面,利用極高局部傳熱係數帶走熱量。 | 傳熱係數可達 250kW/m2K,可冷卻 5500W/cm2 熱通量。 | 定點高效冷卻,適用於極端熱點。 | 冷卻均勻性、流體管理、噴嘴堵塞/侵蝕、整合複雜性、噪音 (氣體噴射)、成本、可擴展性。 |

微型/扁平熱管 | 嵌入式扁平熱管,3D打印熱管 | 利用工作流體在密封腔體內的蒸發-冷凝循環傳遞熱量。 | 等效熱導率可達固體銅的7倍以上。3D打印FOHPFR熱阻降低65.6%。 | 被動式高效傳熱,無需額外功耗。 | 毛細芯結構設計、工作流體選擇、密封性、小尺寸整合難度、嵌入式版本的製造複雜性。 |

導熱孔 (TTSV)/熱收集網路 (TCN) | 銅填充TTSV,BEOL層中的TCN金屬網路 | TTSV提供垂直低熱阻通路,TCN收集並引導熱量至TTSV。 | 可顯著降低晶片最高溫度,熱量吸出效率11-35%。 | 直接從晶片內部移除熱量,針對性強。 | 佔用晶片面積、CTE失配、潛在過熱風險、製造複雜性。 |

彈性設計:熱穩健3D IC的方法學與工具

為了應對先進3D封裝中嚴峻的熱挑戰及其對可靠性的深遠影響,業界正從設計源頭入手,發展一系列重點在提升熱穩健性的方法學和工具。其核心思想是將熱管理和可靠性考量融入到設計流程的早期階段,實現電、熱、力多物理場的協同優化。

3D架構的熱可靠性設計 (DfTR) 原則

熱可靠性設計 (Design for Thermal Reliability, DfTR) 強調在設計初期就主動納入熱和可靠性因素,而非在設計後期進行補救。這需要對晶片的電氣性能、熱行為以及機械應力進行綜合考量和協同優化。

DfTR的關鍵策略包括:

材料選擇: 精心挑選具有合適CTE、高熱導率和良好機械性能的材料,以最大限度地減少熱失配應力,並增強熱量從熱源到散熱器的傳導效率。例如,選擇與矽CTE相近的中介層材料,或採用高導熱的TIM和散熱片。

結構設計: 優化封裝的幾何形狀、各功能層的厚度、TSV的佈局和密度、以及互連佈線的路徑,以有效管理應力分佈,改善散熱通路。例如,透過合理的TSV陣列排布來增強垂直導熱,或設計應力緩衝結構。

功率分配管理: 設計高效的功率傳輸網路 (PDN),以最大限度地減少焦耳熱的產生,並確保穩定的功率供給,避免因電壓降過大導致的局部功耗增加。

熱點緩解: 透過設計手段 (如分散高功耗單元) 或主動管理技術 (如動態電壓頻率調整 DVFS) 來降低峰值溫度,避免局部過熱。

這種從被動應對到主動預測和預防的轉變,是3D IC設計理念的一大進步。鑑於3D IC的複雜性和高昂的重新設計成本,在架構定義和佈局規劃階段就預見並緩解潛在的熱問題,對於確保產品的最終成功至關重要。

熱感知佈局、佈線與佈局策略

在物理設計階段,採用熱感知的佈局 (floorplanning)、佈線 (placement) 和繞線 (routing) 策略,對於優化3D IC的熱特性、減少熱點、管理熱機械應力至關重要,同時還需兼顧線長、性能和面積等傳統設計目標。

具體技術包括:

晶片間的策略性間距: 在2.5D或3D Chiplet整合中,合理地增加高功耗晶片之間的間距,可以有效減少熱串擾和應力集中。

高功耗模組的佈局: 將發熱量大的功能模組放置在靠近冷卻源的位置,或者佈置在具有更優散熱路徑的晶片層上。

TSV陣列的優化: 針對導熱需求,設計專用的導熱TSV (Thermal TSV) 陣列,優化其位置、密度、直徑、間距和深寬比,以增強垂直方向的熱傳導能力。

自動化工具與演算法: 利用先進的EDA工具和優化演算法,如STAMP-2.5D中採用的模擬退火 (simulated annealing) 結合有限元分析 (FEA) 的方法,進行多目標優化,在熱性能、機械應力、線長等多個維度上尋求最佳平衡。

實施這些熱感知設計策略,可以在可接受的線長或面積開銷範圍內,顯著降低晶片的峰值溫度、減緩溫度梯度、並降低機械應力水平,從而提升整體可靠性。

先進熱建模、模擬 (FEA, CFD) 與實驗表徵

由於3D封裝結構的極端複雜性,準確預測其內部溫度分佈、熱流路徑、應力分佈以及長期可靠性,對於設計驗證和優化至關重要。

主要的建模與模擬技術包括:

有限元分析 (FEA): FEA是進行熱機械應力分析、翹曲預測和詳細溫度分佈計算的標準方法。針對大型複雜模型,一些專用求解器 (如XSim) 可以顯著加速FEA的計算過程。

計算流體動力學 (CFD): CFD對於模擬液體冷卻系統 (如微流控、浸沒式冷卻、噴射衝擊冷卻) 和空氣冷卻系統中的流體流動和傳熱現象至關重要。

緊湊熱模型 (Compact Thermal Models, CTMs): CTMs是簡化的等效熱阻-熱容 (RC) 網路模型,用於在設計早期階段或系統級進行快速的熱分析。例如,HotSpot工具就是基於CTM的。針對3D IC,也發展了等效各向異性熱導率模型。

電熱協同模擬: 為了準確捕捉焦耳熱效應以及材料電導率和熱導率隨溫度變化的特性,必須進行電場和熱場的耦合模擬。

主流的商業模擬工具包括:西門子EDA的Calibre 3DThermal、Simcenter Flotherm、HyperLynx;Ansys的通用FEA/CFD求解器;COMSOL的多物理場模擬平台;以及Ansys Icepack等專用電子散熱模擬軟體。

實驗驗證對於校準和確認模擬模型的準確性不可或缺。常用的實驗表徵技術包括:使用專門設計的熱測試晶片 (thermal test chips/vehicles)、整合溫度感測器、紅外熱像儀 (IR thermography)、微區拉曼光譜測溫 (micro-Raman thermography) 進行溫度場測量,以及利用陰影疊紋干涉術 (Shadow Moiré) 測量翹曲等。

模擬、實驗和標準化這三者之間形成了推動技術進步的關鍵循環。先進的模擬工具能夠預測複雜3D結構的行為,指導實驗設計和產品優化。實驗表徵則反過來驗證模擬模型的準確性,並揭示新的物理現象或失效機制。而標準化工作 (如JEDEC標準) 則確保了測試方法的一致性和結果的可比性,為整個產業提供了一個共同的技術基礎和交流平台。目前,針對多裸晶封裝的緊湊熱模型標準尚不完善,這可能是未來標準化工作的一個重點方向,以更好地支援複雜3D IC的熱設計。

標準化 (JEDEC, IEEE路線圖) 在確保熱性能中的作用

標準化在推動和規範先進封裝熱管理技術的發展中扮演著重要角色。

JEDEC標準: JEDEC固態技術協會制定了一系列關於封裝半導體器件熱測試和表徵的標準,如JESD51-X系列。這些標準定義了通用的熱測試方法 (如結到環境熱阻 θJA、結到外殼熱阻 θJC、結到板級熱阻 θJB 的測量)、測試板的設計規範以及數據報告格式,重點在為不同供應商提供的器件熱性能比較提供一個公平的基準。

對3D/多裸晶封裝的適用性: 傳統的JEDEC標準主要針對單裸晶封裝。雖然JESD51-31和JESD51-32等標準對多裸晶封裝的數據報告和測試板設計進行了擴展,但在應對複雜3D IC的獨特挑戰方面,特別是在緊湊熱建模方面,仍存在不足。未來可能需要針對3D IC的降階模型 (Reduced Order Models, ROMs) 制定新的標準,以方便在系統級設計中進行高效的熱分析。

IEEE路線圖 (如異質整合路線圖 - HIR): IEEE等產業組織發布的技術路線圖,如異質整合路線圖 (HIR),對異質和3D整合中的熱管理等關鍵挑戰、發展需求和未來方向進行了梳理和展望,為學術研究和產業發展提供了重要的指導。這些路線圖有助於凝聚產業共識,引導研發資源投向關鍵領域。

產業會議 (ECTC, ITherm): 電子元件技術會議 (ECTC) 和半導體熱測量、建模與管理研討會 (ITherm) 等專業學術會議,為全球研究人員和工程師提供了一個交流最新研究成果、探討技術挑戰、促進在熱管理和封裝技術領域合作的重要平台。

3D IC設計中涉及的變量眾多,且優化目標之間往往存在衝突 (如散熱、機械應力、電氣性能、成本、面積等)。人工進行多目標優化幾乎是不可能的。因此,自動化的佈局規劃工具,如STAMP-2.5D,以及由AI驅動的設計平台,正成為應對這些複雜權衡的關鍵賦能技術。這些工具能夠探索更廣闊的設計空間,找到平衡多個目標的優化或近優化解決方案,對於設計具有彈性的3D IC至關重要。

產業視角:領導廠商及其技術路徑

全球主要的半導體製造商和封裝廠都在積極投入資源,開發各自獨特的先進3D封裝技術平台,以應對日益增長的性能需求和散熱挑戰。這些技術不僅代表了產業的最高水平,也揭示了未來發展的趨勢。

台積電 (TSMC):CoWoS、SoIC與整合型扇出 (InFO)

台積電作為全球領先的晶圓代工廠,其在先進封裝領域的佈局尤為引人注目,旗下擁有多個成熟且不斷演進的技術平台。

CoWoS (Chip-on-Wafer-on-Substrate): CoWoS是台積電一款成熟的2.5D封裝技術,主要應用於高性能計算 (HPC) 和人工智慧 (AI) 等領域,用於整合邏輯晶片和高頻寬記憶體 (HBM)。其技術路線圖包括不斷增大中介層的尺寸 (如CoWoS-XL),並引入了諸如整合電容 (Integrated Capacitors, iCAPs) 等創新技術。iCAPs透過在矽中介層中整合深溝槽電容,能夠顯著改善功率傳輸網路 (PDN) 的阻抗,從而提升電源完整性,並可能間接帶來散熱效益。

SoIC (System-on-Integrated-Chips): SoIC是台積電在3D堆疊領域的旗艦技術,屬於前端製程範疇。它採用直接銅對銅 (Cu-to-Cu) 混合鍵合技術,實現了次10微米等級的超細間距垂直互連,無需傳統的微凸塊。SoIC重點在提供極高的性能、更低的功耗以及更優的電源和訊號完整性。它支援晶片對晶圓 (CoW) 和晶圓對晶圓 (WoW) 兩種方案,並且可以與CoWoS和InFO等後端封裝技術相結合,實現所謂的「3Dx3D」系統級整合。NVIDIA、AMD和Apple等頂級晶片設計公司均已宣布在其下一代產品中採用SoIC技術。

COUPE (Compact Universal Photonic Engine): 針對光電共封裝 (Co-Packaged Optics, CPO) 的需求,台積電推出了COUPE平台。該平台利用SoIC-X (SoIC的一種變體) 技術,將電晶片 (EIC) 直接堆疊在光子晶片 (PIC) 之上,以最大限度地縮短電氣連接路徑,提升能源效率和降低延遲。然而,將高功耗的EIC堆疊在對熱敏感的PIC之上,帶來了嚴峻的散熱挑戰。可能的解決方案包括液體冷卻、導熱通孔和高效散熱片等。

整合型扇出 (InFO): InFO是台積電另一項重要的扇出型封裝技術,主要應用於移動處理器等對成本和尺寸敏感的領域。

在熱管理方面,雖然具體的白皮書未在提供的資料中出現,但SoIC和CoWoS等高密度、高性能封裝技術的發展,本身就驅動著對先進散熱方案的迫切需求。SoIC的無凸塊直接鍵合技術被認為比傳統3D封裝具有更好的散熱特性,但精確的熱分析仍然至關重要。

英特爾 (Intel):Foveros、EMIB與光電共封裝

英特爾作為一家整合元件製造商 (IDM),在先進封裝領域同樣擁有深厚的技術積累和清晰的戰略佈局。

Foveros: Foveros是英特爾的3D裸晶堆疊技術,其核心思想是將不同功能、不同製程的晶片進行垂直整合。Foveros技術有多種演進版本,例如Foveros Omni採用銅柱 (copper columns) 代替TSV進行垂直訊號傳輸,而Foveros Direct則採用銅對銅混合鍵合,實現了更小的凸塊間距 (≤5微米),適用於記憶體與邏輯晶片的緊密堆疊。

EMIB (Embedded Multi-die Interconnect Bridge): EMIB是英特爾的2.5D封裝技術,其特點是採用局部嵌入的小型矽橋接裸晶 (silicon bridge die) 來實現高頻寬的裸晶間互連,避免了使用大面積矽中介層所帶來的成本和散熱限制。EMIB-T是EMIB的增強版本,在橋接裸晶中加入了TSV,支援垂直方向的訊號和功率傳輸,對於AI工作負載中的高頻寬記憶體訪問至關重要。

熱管理與創新:

EMIB的局部化橋接設計,相較於傳統的大面積矽中介層,有助於更好地管理熱量和降低熱應力。

針對EMIB-T的EDA設計流程中,已包含對裸晶、橋接裸晶和封裝基板的詳細熱分析。

Foveros技術允許對堆疊中的每一層進行獨立優化,這為熱設計提供了更大的靈活性。例如,可以將對熱不敏感的I/O裸晶放置在計算裸晶下方。

英特爾也在積極研發光電共封裝技術,這類應用同樣面臨著嚴峻的熱管理需求。3D堆疊中裸晶間的熱阻和熱串擾是其面臨的主要挑戰。

三星 (Samsung):X-Cube、I-Cube與H-Cube

三星作為全球主要的記憶體和邏輯晶片製造商之一,也在先進封裝技術方面持續投入,推出了X-Cube、I-Cube和H-Cube等系列解決方案。

X-Cube: X-Cube是三星的3D IC堆疊技術,重點在實現高頻寬、低功耗的垂直整合,並降低大尺寸單片晶片的良率風險。X-Cube技術最初基於微凸塊連接,目前正在積極開發混合銅鍵合 (Hybrid Copper Bonding, HCB) 技術,目標是實現小於4微米的鍵合間距。HCB技術透過消除傳統凸塊間的間隙,有望顯著改善互連密度和熱性能。

I-Cube & H-Cube: I-Cube和H-Cube是三星的2.5D封裝解決方案。I-Cube採用平行的水平晶片佈局,有助於分散熱量,應對散熱挑戰。I-CubeS版本進一步提升了熱效率控制和翹曲控制能力。H-Cube則更側重於在堆疊多個邏輯晶片和HBM時,透過其專有的訊號/電源完整性技術,確保穩定的功率供給並最大限度地減少訊號損失和失真,這間接有助於熱管理。

熱性能提升: 三星強調其封裝技術在熱性能方面的提升。例如,I-Cube的水平佈局有助於散熱。X-Cube的混合銅鍵合被認為能透過消除接合間隙來提高熱性能。

封測代工廠 (OSATs) 的角色:以日月光 (ASE) 為例

除了晶圓代工廠和IDM廠商,專業的封測代工廠 (Outsourced Semiconductor Assembly and Test, OSATs) 在先進封裝領域也扮演著日益重要的角色。它們通常提供更廣泛的封裝選擇和更靈活的服務。

日月光 (ASE) 的技術佈局: 日月光作為全球領先的OSAT廠商,在先進封裝領域擁有全面的技術組合,包括針對高功率和高速應用的基板技術。其VIPack™平台是一個可擴展的先進封裝解決方案組合,目的在滿足AI、HPC等高性能應用的需求。

FOCoS (Fan-Out Chip-on-Substrate): FOCoS是日月光的一種扇出型封裝技術,它將扇出封裝體 (包含透過RDL互連的多個晶片) 再以倒裝焊的方式安裝到高引腳數的BGA基板上。FOCoS重點在提供相對於2.5D中介層方案更低的成本、更薄的封裝厚度以及良好的電氣性能。FOCoS有多種變體,如FOCoS-CF (Chip First) 和FOCoS-CL (Chip Last),以及整合了矽橋接裸晶的FOCoS-Bridge,適用於ASIC與HBM的整合。

熱管理與可靠性研究: 日月光在其技術論文和博客中討論了其封裝方案的熱機械性能。例如,有研究分析了FOCoS平台中RDL層數增加對翹曲和應力的影響,指出基板和封裝蓋材料的選擇對控制整體封裝翹曲更為關鍵,而RDL層的應力則受基板CTE的影響較大。另一項研究比較了不同類型扇出封裝 (如eWLB, M-Series™, FOCLP) 的機械和熱性能,結果顯示不同扇出封裝的熱性能相似,且整體優於傳統的WLCSP。日月光也強調其在電源模組封裝方面的熱管理能力,包括採用更薄的裸晶設計、先進的裸晶貼裝材料 (如銀漿或銅漿燒結) 以及改進的封裝內部連接 (如銅夾片焊接) 來降低熱源和熱阻。

光電共封裝 (CPO): 日月光也展示了其在CPO領域的創新,重點在將光學引擎直接整合到交換晶片封裝中,以實現最短的電氣路徑和顯著的功耗節省,這對於應對數據中心日益增長的頻寬和能效需求至關重要。

這些產業領導者在先進3D封裝技術上的持續投入和創新,不僅推動了半導體性能的提升,也對整個電子產業的發展方向產生深遠影響。它們各自的技術路徑和解決方案,反映了對市場需求、技術挑戰以及自身核心競爭力的不同理解和側重。一個共同的趨勢是,這些廠商不僅僅提供單一的封裝技術,更在構建一個包含設計套件、EDA工具支援和產業鏈合作夥伴在內的完整生態系統。這種生態系統的實力,正日益成為衡量其在先進封裝領域競爭力的重要指標。

研究機構的角色:以IMEC為例

除了業界巨頭,比利時微電子研究中心 (IMEC) 等領先的獨立研究機構也在推動先進3D封裝及其熱管理技術的發展中扮演著關鍵角色。它們通常專注於前瞻性的基礎研究和共性技術的開發,為整個產業提供創新思路和解決方案。

IMEC在3D整合與冷卻領域的研究: IMEC在3D系統整合,特別是3D互連技術 (如混合鍵合) 和先進冷卻方案方面有著深入的研究。

先進液體冷卻研究: IMEC正與魯汶大學 (KU Leuven) 合作,開發和優化用於微晶片的先進液體冷卻技術,重點研究噴射衝擊冷卻和微通道液體冷卻,並探索利用增材製造 (AM) 技術製造陶瓷 (如SiC) 冷卻器的可能性。該研究計劃包括:

冷卻器設計與優化: 利用CFD模擬,研究噴嘴直徑、間距、通道尺寸等參數對熱流體性能的影響,並結合製造約束進行優化。

增材製造與激光表面處理: 探索用於製造陶瓷SiC冷卻器的AM技術,並應用激光表面處理來改善表面粗糙度等特性。

熱與機械表徵: 使用帶有整合熱元件和感測器的定制微晶片,在熱測試平台上對冷卻器進行熱性能表徵 (如溫度分佈、傳熱效率),並與模擬結果進行比較驗證。同時,進行機械測試以評估熱介面的可靠性 (如冷卻器與微晶片間的附著強度),並研究熱循環和機械應力對介面完整性的影響。

光電共封裝 (CPO) 的熱挑戰: IMEC也關注CPO技術中的熱管理問題。如前所述,將高功耗的EIC堆疊在對熱敏感的PIC之上,會帶來嚴峻的散熱挑戰。IMEC的研究有助於探索解決這些問題的創新方案。

混合鍵合的推進: IMEC在推進混合鍵合技術的成熟度和可製造性方面也做出了重要貢獻,這對於實現更高密度的3D整合至關重要,而更高密度又反過來加劇了散熱需求。

研究機構如IMEC的工作,通常具有更強的探索性和基礎性,它們的研究成果往往能夠為整個產業提供新的技術方向和解決方案原型,彌合基礎科學發現與工業化應用之間的差距。

未來展望:熱管理與可靠性的持續挑戰與機遇

隨著半導體技術向著更高整合度、更高性能和更多樣化功能的方向持續演進,先進3D封裝在未來電子系統中的核心地位將日益凸顯。然而,與此同時,熱管理和可靠性問題也將持續構成嚴峻的挑戰,並不斷催生新的研究方向和技術機遇。

IEEE異質整合路線圖 (HIR) 對熱管理的發展需求

IEEE異質整合路線圖 (HIR) 為產業指明了未來發展方向,其中熱管理被列為關鍵的賦能技術之一。HIR強調了以下幾個核心的發展需求:

先進建模與模擬技術: 需要更精確、更高效的建模工具來預測和管理複雜異質整合封裝內的熱流分佈、熱點位置和熱機械應力。這對於在設計早期識別潛在問題、優化晶片佈局和散熱方案至關重要。

新型高性能材料: 迫切需要開發兼具高熱導率和低電導率的新型材料。高熱導率有助於快速散熱,而低電導率則避免對晶片電氣性能造成干擾。潛在的候選材料包括鑽石、氧化鈹、氮化鋁、氮化硼及其複合材料。此外,針對TIM和散熱片,也需要開發具有更優熱性能和長期可靠性的新材料。

創新的整合冷卻解決方案: 需要能夠無縫整合到複雜封裝結構中的新型冷卻方案。這包括3D TIMs (能夠適應不均勻表面並提供高效導熱)、CTE匹配的散熱片 (以減少熱應力並均勻散熱),以及更先進的嵌入式冷卻技術,如微流控、熱管等。

高堆疊數3D IC的可靠性挑戰

隨著3D IC向更高堆疊層數發展 (例如,HBM已發展到12層,未來可能達到16層甚至更多),其可靠性面臨的挑戰也隨之升級:

極端功率密度與散熱極限: 在AI加速器和量子處理器等應用中,高堆疊數3D IC的功率密度可能超過 100W/cm2,甚至挑戰 200W/cm2 以上的散熱極限。傳統TIM在此熱流密度下可能失效,迫使業界尋求更激進的冷卻方案,如整合微流控通道或晶片上熱電致冷器 (TECs)。然而,這些先進冷卻方案的整合又會帶來面積開銷和製造複雜性的問題。

TSV及鍵合的累積良率損失: 儘管單步的TSV製造和晶片鍵合良率可能很高,但在高堆疊數的情況下,每一步微小的失效率都會被放大,導致最終堆疊體的整體良率顯著下降。例如,即使單步鍵合成功率為99.99%,一個12層的3D IC在每步鍵合中仍會遭受0.12%的堆疊良率損失,這對於大尺寸裸晶而言可能是災難性的。為此,研究方向包括開發具有自修復能力的介面材料 (如利用奈米級液態金屬液滴),以及採用Chiplet模組化設計和冗餘互連通路來提高整體系統的容錯能力。

熱機械應力的加劇: 更多的堆疊層數表示更複雜的材料組合和更長的熱傳導路徑,這使得由於CTE失配引起的熱機械應力問題更加突出,更容易導致翹曲、分層和疲勞失效。

Chiplet異質整合的未來熱機械協同設計挑戰

Chiplet異質整合是未來半導體發展的重要趨勢,但它也帶來了獨特的熱機械協同設計挑戰。

CTE失配的複雜化: 在一個封裝內整合來自不同製程節點、不同材料 (如矽、III-V族、玻璃)、不同尺寸的Chiplet,使得CTE失配問題變得異常複雜。緊密堆疊這些Chiplet會產生巨大的熱應力,危及封裝的長期可靠性。

熱串擾與熱隔離: 不同Chiplet之間可能存在巨大的功耗差異和溫度敏感性差異。如何有效地管理高功耗Chiplet產生的熱量,避免其對相鄰的低功耗或對溫度敏感的Chiplet (如記憶體、模擬電路、光子器件) 造成不利影響,是熱設計的關鍵。這需要在Chiplet佈局規劃階段就充分考慮熱性能、機械應力和互連效率的平衡。

自動化協同優化工具的需求: 傳統上優先考慮線長縮減的物理設計方法,在Chiplet系統中可能會導致熱瓶頸和CTE失配加劇。因此,迫切需要能夠同時優化熱性能、機械應力和互連效率的自動化佈局規劃工具。STAMP-2.5D等研究成果展示了這類工具的潛力,它們透過有限元分析模擬溫度和應力分佈,並結合優化演算法 (如模擬退火) 來尋找最佳的Chiplet佈局方案。實驗結果表明,這種熱結構感知的方法可以在保持優異熱性能的同時,顯著降低整體應力和互連線長。

未來,隨著光子整合、量子計算等新興技術與半導體封裝的進一步融合,熱管理和可靠性問題將呈現出新的特點和更高的複雜性。例如,光子器件對溫度極為敏感,其與高功耗電子晶片的共封裝對熱隔離和精確溫控提出了極高要求。

總體而言,「超越摩爾定律」時代的性能追求與封裝體物理極限之間的張力,將持續定義未來熱管理技術的創新方向。3D IC的可靠性不再僅僅是溫度的問題,而是熱、力、電等多物理場在從材料介面到系統層級的多尺度上複雜交互作用的結果。因此,跨越材料科學、晶片架構、封裝結構和冷卻系統的協同設計,並藉助AI和多目標優化工具的輔助,將是應對這些持續挑戰、抓住未來機遇的必由之路。

JEDEC熱標準在3D IC封裝中的演進與挑戰

JEDEC JC-15委員會致力於制定熱標準,為產生熱特性數據提供通用參考點,確保測試結果的一致性和科學性。這些標準涵蓋了單裸晶和多裸晶封裝的熱阻測量、LED熱特性以及基於模擬的JEDEC標準,如用於創建簡化熱網路模型的方法。

JESD51-31對單裸晶封裝標準進行了擴展,納入了多裸晶封裝數據報告的方法,並提出了在多個位置感測外殼溫度的建議。JESD51-32則針對多裸晶封裝導致引線數量受限的情況,對測試板設計進行了擴展。

然而,為多裸晶封裝創建緊湊熱模型 (CTM) 極具挑戰性。儘管封裝模擬軟體供應商已開發出降階模型 (ROM),但目前尚無針對ROM的JEDEC標準。隨著模擬軟體在生成多晶片模組 (MCM) ROM方面的日益普及,預計未來將需要新的ROM標準,以便在封裝供應商和系統設計者之間提供一個通用的數據交換框架。這表明JEDEC標準仍在不斷發展,以應對先進封裝技術 (包括3D IC) 帶來的獨特熱測試和表徵挑戰。

結論

先進3D封裝技術,作為延續半導體產業發展、突破摩爾定律瓶頸的關鍵路徑,正以前所未有的速度推動著人工智慧、高性能計算、新一代通訊等領域的變革。然而,這種將多個功能單元在三維空間內極致整合的範式,也將熱管理和可靠性問題推向了風口浪尖。高聳的功率密度、叢生的局部熱點、迷宮般複雜的散熱路徑以及無處不在的熱串擾,共同構成了3D封裝的「散熱夢魘」。在此嚴峻的熱應力環境下,材料老化、熱機械應力引發的翹曲、開裂、分層,以及電遷移導致的互連失效等可靠性問題層出不窮,嚴重制約著3D IC性能的充分發揮和長期穩定運行。

面對這一系列挑戰,學術界和工業界展現出巨大的創新活力。從優化傳統的熱介面材料和散熱片,到開發碳奈米材料、鑽石等具有顛覆性熱性能的新型材料;從改進TSV導熱設計,到探索微流控、浸沒式冷卻、噴射衝擊冷卻、嵌入式熱管等激進的冷卻技術;從熱感知佈局、多物理場協同仿真,到建立標準化的測試與表徵方法,一個多維度、多層次的熱管理與可靠性保障體系正在逐步構建。

值得注意的是,解決3D封裝的熱與可靠性問題,並非單一技術的突破所能達成,而是一個系統工程。它需要材料科學家、晶片架構師、封裝工程師、散熱專家以及EDA工具開發者之間的緊密協作。未來,隨著Chiplet異質整合的進一步深化和堆疊層數的持續增加,熱機械協同設計的複雜性將與日俱增,對自動化、智能化設計工具的需求也將更加迫切。

總而言之,儘管先進3D封裝的散熱與可靠性之路充滿荊棘,但持續的技術創新和跨學科合作,正不斷為我們照亮前行的方向。成功駕馭這場「散熱夢魘」,將是釋放3D整合全部潛力、開啟下一個計算時代的關鍵所在。

留言