【科技速解】CoWoS 與先進封裝:摩爾定律的續命丹,晶圓代工的新戰場

- 2月11日

- 讀畢需時 4 分鐘

秒懂重點:為什麼你現在非懂不可?

過去五十年,半導體業的遊戲規則很簡單:把電晶體做得越小越好(例如從 7 奈米變成 3 奈米),但現在,這條路撞牆了。物理學告訴我們,原子不能無限分割,且越小的晶片越貴、良率越低。

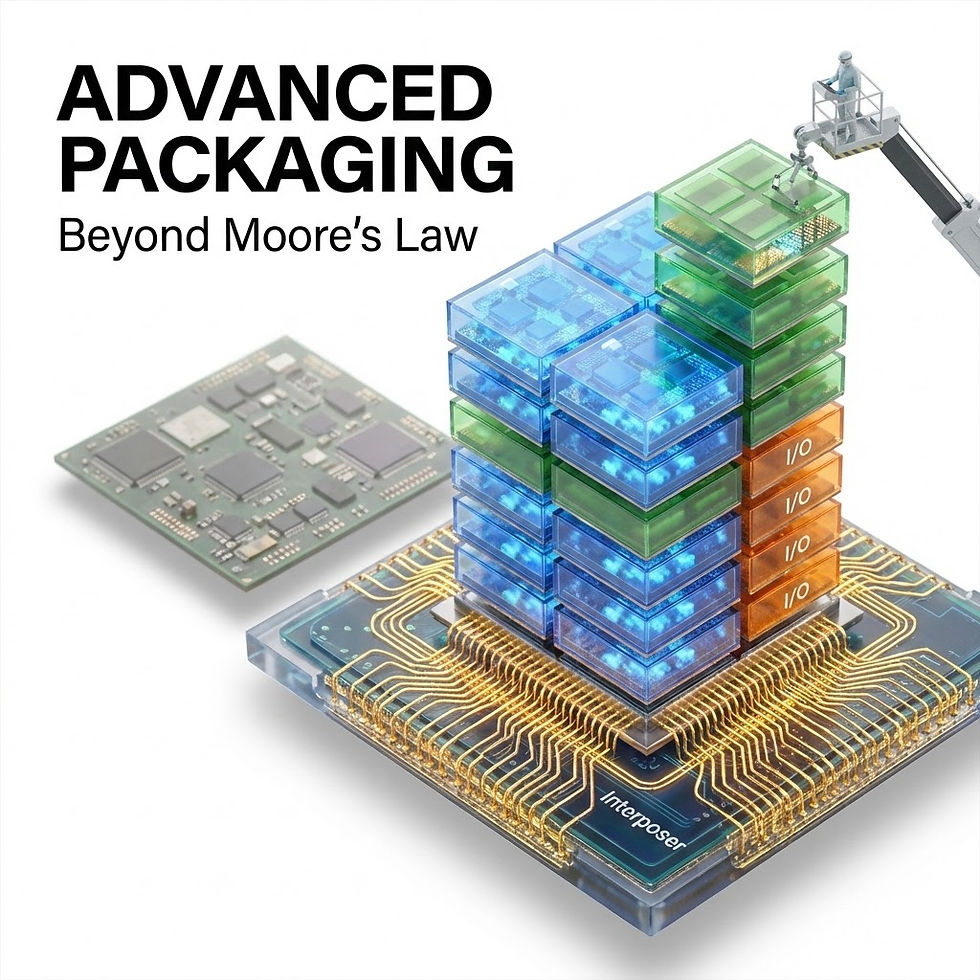

然而,AI 對算力的渴望是無底洞,既然「單顆晶片」做不大也做不快了,工程師們想出了一個暴力解法:「把不同的晶片像樂高積木一樣拼起來,甚至疊起來。」

這就是「先進封裝 (Advanced Packaging)」的核心概念,也是台積電 CoWoS (Chip on Wafer on Substrate) 技術的精髓,現在的投資邏輯已經改變:誰能把晶片「封」得好,誰才是老大,這導致了傳統封測廠 (OSAT) 與晶圓代工廠 (Foundry) 的界線模糊化,更創造了全新的設備供應鏈商機(如濕製程、貼合機、檢測設備),簡單說,以前封裝是「包裝紙」,現在封裝是「大腦神經網路」的一部分。

技術白話文:原理解析與核心突破

要理解先進封裝,我們得先釐清「前段 (Front-end)」與「後段 (Back-end)」的關係。

過去的瓶頸:它解決了什麼關鍵問題?

光罩尺寸限制 (Reticle Limit): 半導體設備能曝光的最大面積是固定的,AI 晶片想塞進更多電晶體,面積卻不能無限擴大。

良率的詛咒: 晶片越大,上面出現瑕疵的機率就越高,做一顆超大晶片,可能壞一點點就整顆報廢(成本極高);但如果切成四顆小晶片,壞一顆只要丟一顆。

傳輸速度: 記憶體 (DRAM) 離運算核心 (GPU) 太遠,數據在電路板上跑太慢,造成「記憶體牆 (Memory Wall)」。

它是如何運作的?(樂高積木與摩天大樓)

先進封裝技術(特別是 2.5D 與 3D IC)可以用「城市規劃」來比喻:

1. 傳統封裝 (2D Packaging) —— 郊區透天厝 晶片像是散落在郊區的平房,彼此之間隔著遙遠的馬路(電路板 PCB),數據要從 A 家跑到 B 家,必須開車經過長長的馬路,速度慢、耗油(耗電)。

2. CoWoS (2.5D Packaging) —— 此路是我開的快速道路 CoWoS 的關鍵在於一個叫做 「中介層 (Interposer)」 的東西。

運作方式: 我們不把晶片直接放在電路板上,而是先把它們並排放在一塊特製的矽基板(中介層)上,這個中介層裡面預埋了比頭髮還細數百倍的「超高速光纖網路」(高密度線路)。

效果: GPU(運算大腦)和 HBM(高頻寬記憶體)就像是搬進了同一個社區,中間有專屬的地下通道相連。數據傳輸速度瞬間提升數十倍。

3. 3D IC (SoIC) —— 垂直摩天大樓 這更激進,直接把晶片「疊」在晶片上面,就像在蓋摩天大樓,電梯(TSV 矽穿孔)直接貫穿樓層。距離最短,傳輸最快,但散熱最難。

為什麼這是革命性的? (Chiplet 小晶片時代)

這催生了 Chiplet (小晶片) 的商業模式,以前買電腦要買整台「旗艦機」;現在廠商可以像組裝樂高一樣:

運算核心用最貴的 3 奈米製程。

I/O 控制器用便宜的 12 奈米製程。

記憶體向美光買。 最後用先進封裝把它們「黏」在一起,變成一顆超級晶片,這大幅降低了設計成本 (NRE) 並提升了良率。

產業影響與競爭格局

先進封裝的崛起,讓「封裝」這個原本毛利低、技術門檻低的產業,變成了高科技軍備競賽。

誰是主要玩家?(供應鏈解析)

晶圓代工廠 (The Kings):

TSMC (台積電): CoWoS 技術的獨霸者,目前 NVIDIA 所有的高階 AI 晶片都非台積電不封,台積電不再只是「造」晶片,更一手包辦了「封」晶片的高階利潤。

Intel (英特爾): 擁有 Foveros 技術,試圖透過先進封裝在晶圓代工市場彎道超車。

設備供應商 (The Arms Dealers): 這是台系廠商的機會。

濕製程設備 (Wet Process): 如 弘塑 (Grand Plastic)、辛耘 (Scientech),因為中介層需要大量的清洗與蝕刻,這些設備的需求量與 CoWoS 產能直接掛鉤。

貼合設備 (Bonder): 要把晶片精準地疊在一起,誤差不能超過 1 微米,荷蘭的 Besi 是混合鍵合 (Hybrid Bonding) 的霸主,但台廠也在追趕。

切割合光 (Dicing & Grinding): 日本 Disco 是絕對龍頭,晶片疊越厚,就需要磨得越薄、切得越精準。

封測廠 (OSAT) 的轉型:

日月光 (ASE): 雖然高階 CoWoS 被台積電拿走,但中階的先進封裝 (Fan-out) 依然是日月光的天下,隨著技術外溢,OSAT 廠將承接大量中階 AI 晶片訂單。

技術的普及時程與挑戰

現在: 產能極度短缺。NVIDIA H100 的交貨期 (Lead Time) 長達 52 週,主因就是卡在 CoWoS 產能。

未來挑戰: 散熱 (Heat Dissipation),當你把晶片疊得像三明治一樣,中間那層的熱量很難散出來,這也連結到了我們上一篇談的「液冷技術」的重要性。

潛在的風險與替代方案

玻璃基板 (Glass Substrate): Intel 正大力推動用「玻璃」取代目前的「有機載板」或「矽中介層」,玻璃更平、更硬、能鑽更細的孔。如果技術成熟,可能會顛覆現有的封裝材料供應鏈。

未來展望與投資視角 (結論)

先進封裝宣告了「後摩爾定律時代」的正式來臨,從投資視角來看,請關注「含金量」的轉移:

CapEx 暴增區: 晶圓廠在後段封裝的資本支出 (CAPEX) 佔比正在歷史性地提升,跟著台積電買設備(弘塑、辛耘、萬潤)是過去一年的顯學,未來則要看誰能切入「檢測 (Metrology)」與「混合鍵合 (Hybrid Bonding)」這塊更高階的市場。

良率即毛利: 先進封裝的良率目前仍低於前段製程,誰能提供提升良率的解決方案(例如自動光學檢測 AOI),誰就能享有高溢價。

生態系綁定: Chiplet 時代,晶片設計將更依賴封裝廠的生態系(如 UCIe 標準)。

未來的晶片戰爭,不只比誰的奈米數字小,更比誰能把積木疊得高、疊得穩。

如果您覺得這篇「晶片樂高學」有讓您秒懂先進封裝的奧義,能不能請您動動手指幫忙分享或按個讚?您小小的鼓勵,是支撐這個小站繼續為大家解碼硬核科技的最大動力!

留言